## Sequential logic design

## Vikas Dhiman for ECE275

November 21, 2022

## 1 Objectives

- 1. Analyse and design both Mealy and Moore sequential circuits with multiple inputs and multiple outputs

- 2. Convert between Mealy and Moore designs

## 2 Mealy vs Moore Finite State Machines

**Definition 1** (Finite State Machines (FSM)). [1, Sec 3.4]

FSM is another name for sequential circuits. FSM is defined in opposition to Infinite State Machines (Turing Machines).

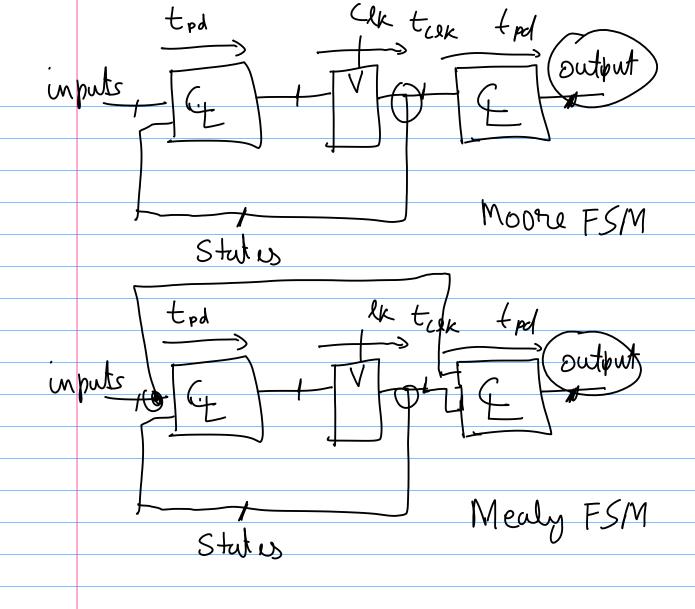

**Definition 2** (Mealy FSM). [1, Sec 3.4.3]

Mealy FSM have outputs that depend up on both inputs and the state of the circuit or the FSM.

**Definition 3** (Moore FSM). [1, Sec 3.4.3]

Moore FSM have outputs that depend only upon the states of the FSM.

seal atutor

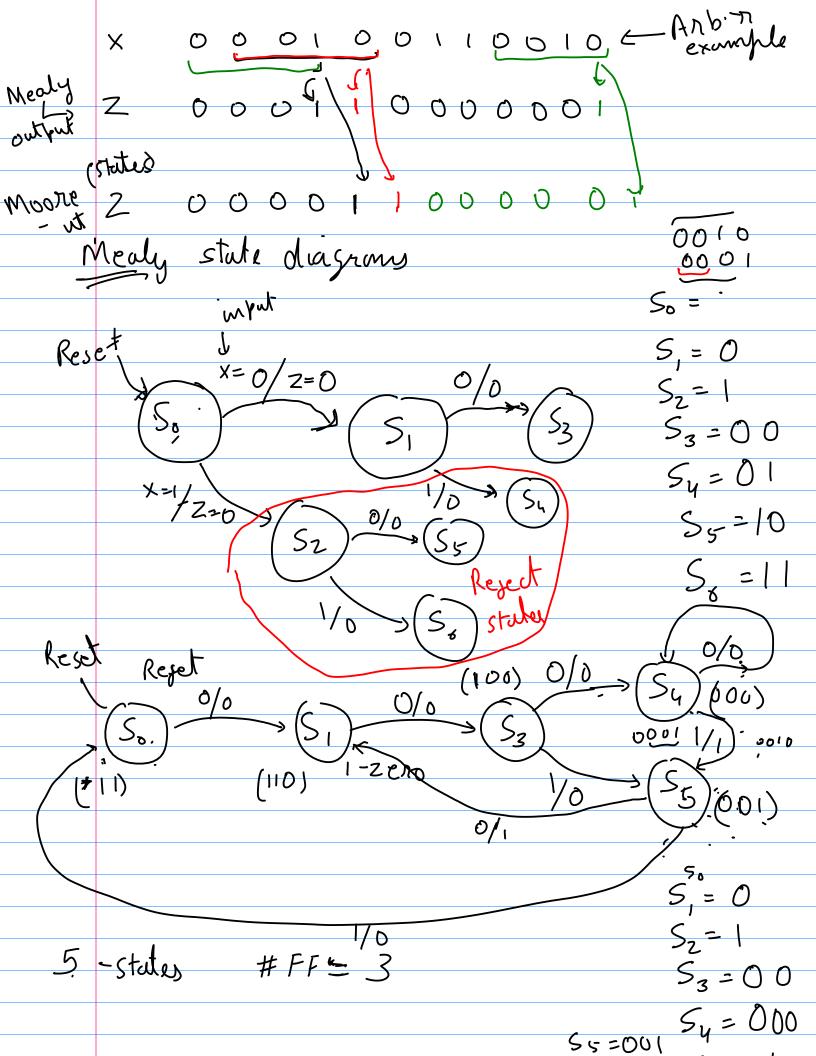

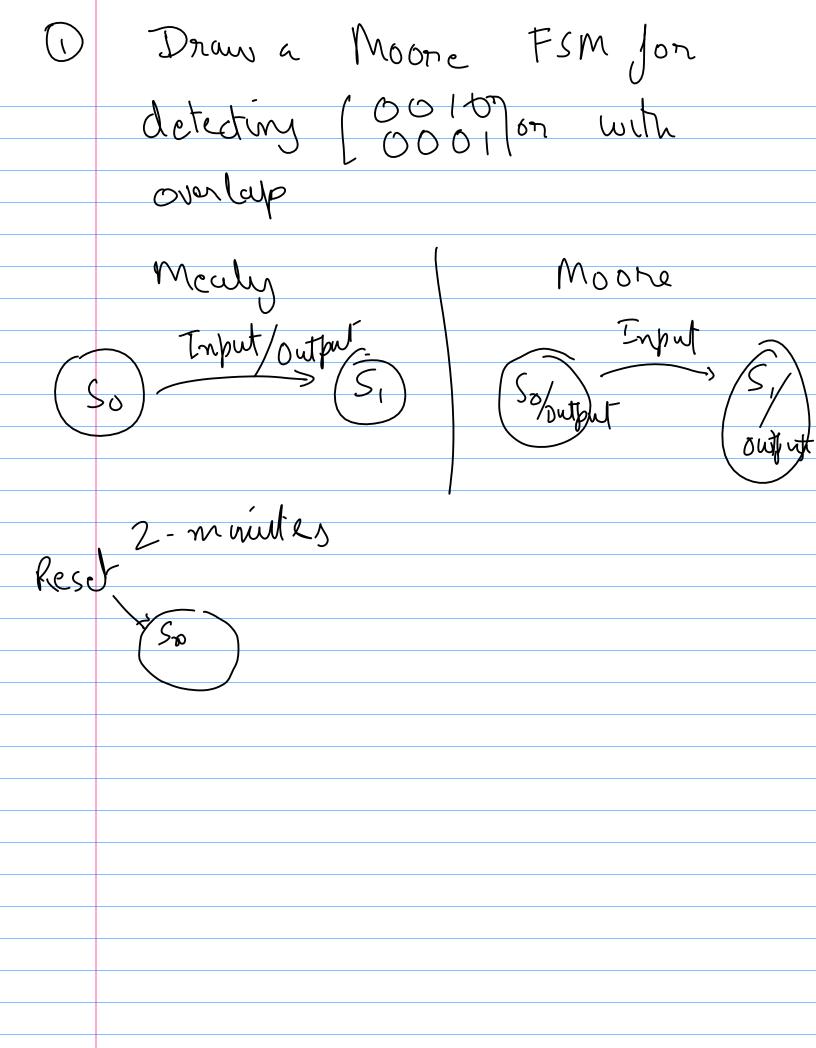

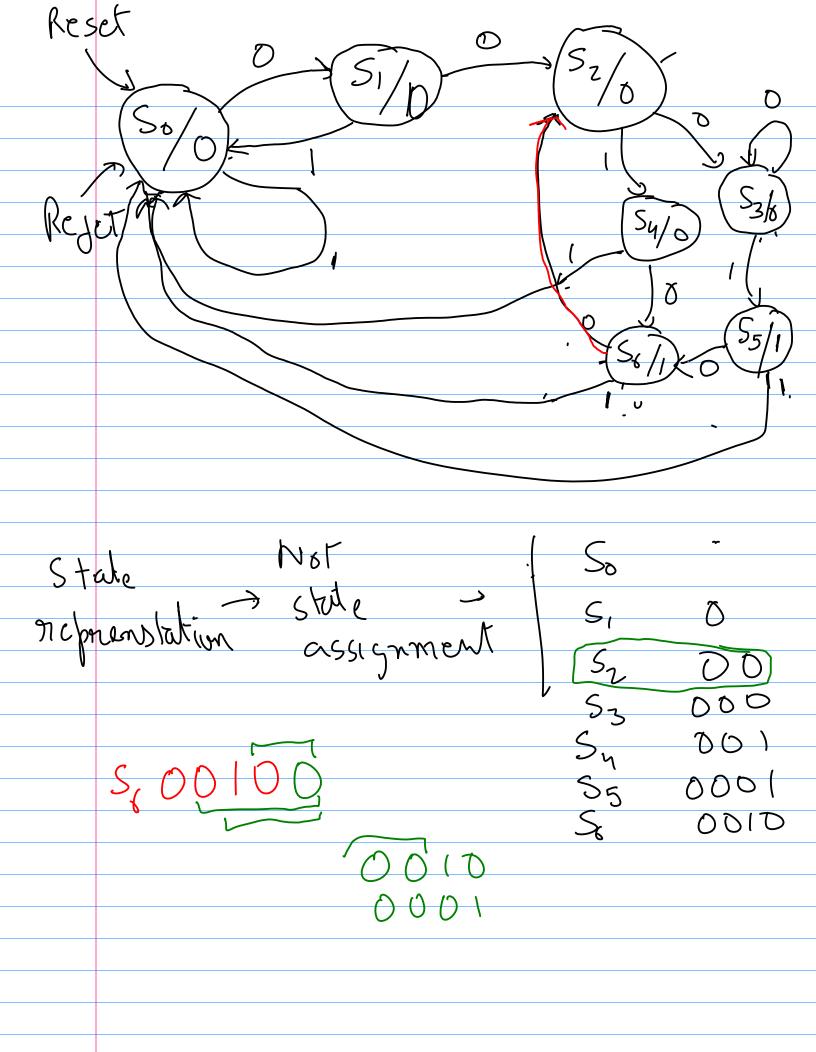

**Example 1.** A sequential circuit has one input (X) and one output (Z). The circuit examines groups of four consecutive inputs and produces an output Z=1 if the input sequence (0.010) or (0.001) occurs. The sequences can overlap. Draw both Mealy and Moore timing diagrams. Find the Mealy and Moore state graph.

000 000

0010] Z=1 X — Status Segrential otherwise Z=D 00100110010 E Anbitrario C) (1 X 00001/1000001 Mealy Z moore 1 100 troftun 0 11 00 170  $M_{0}$ X 0 111 0 000 0 1011 Medy Z 600001000000000 Moone Z Mealy FSM Output depends on both state+mput Moore FSM Output depends on state only

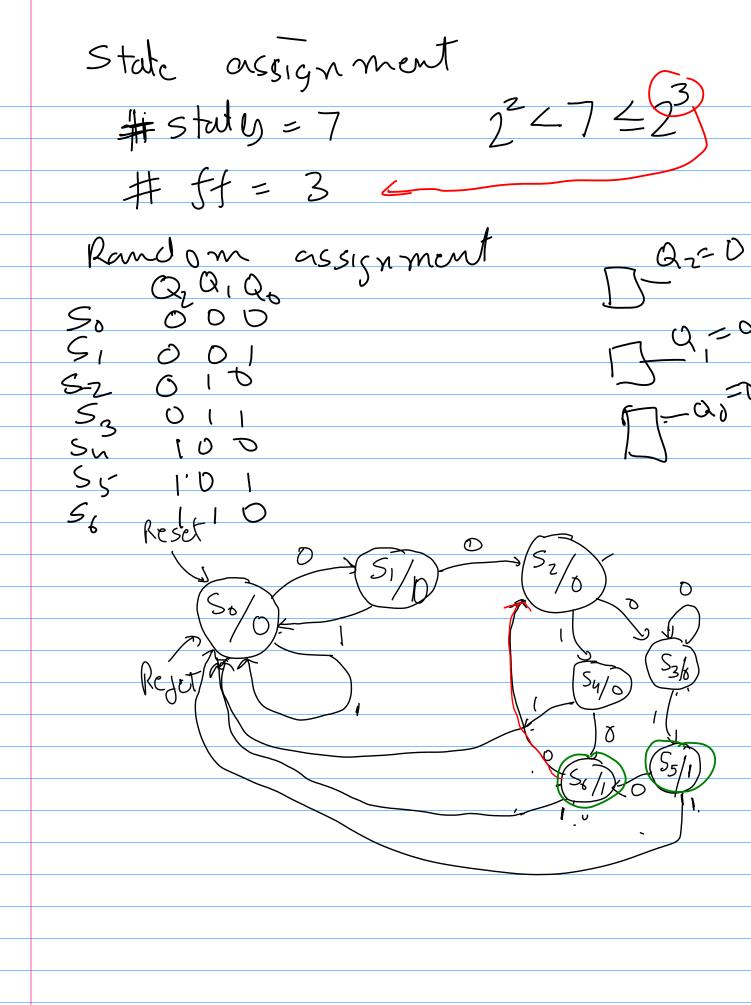

**Practice Problem 1.** A sequential circuit has one input (X) and one output (Z). The circuit examines groups of four consecutive inputs and produces an output Z=1 if the input sequence 0101 or 1001 occurs. The circuit resets after every four inputs. Draw both Mealy and Moore timing diagrams. Find the Mealy and Moore state graph.

Inputs

References

[1] Sarah L Harris and David Harris. Digital design and computer architecture. Morgan Kaufmann, 2022.

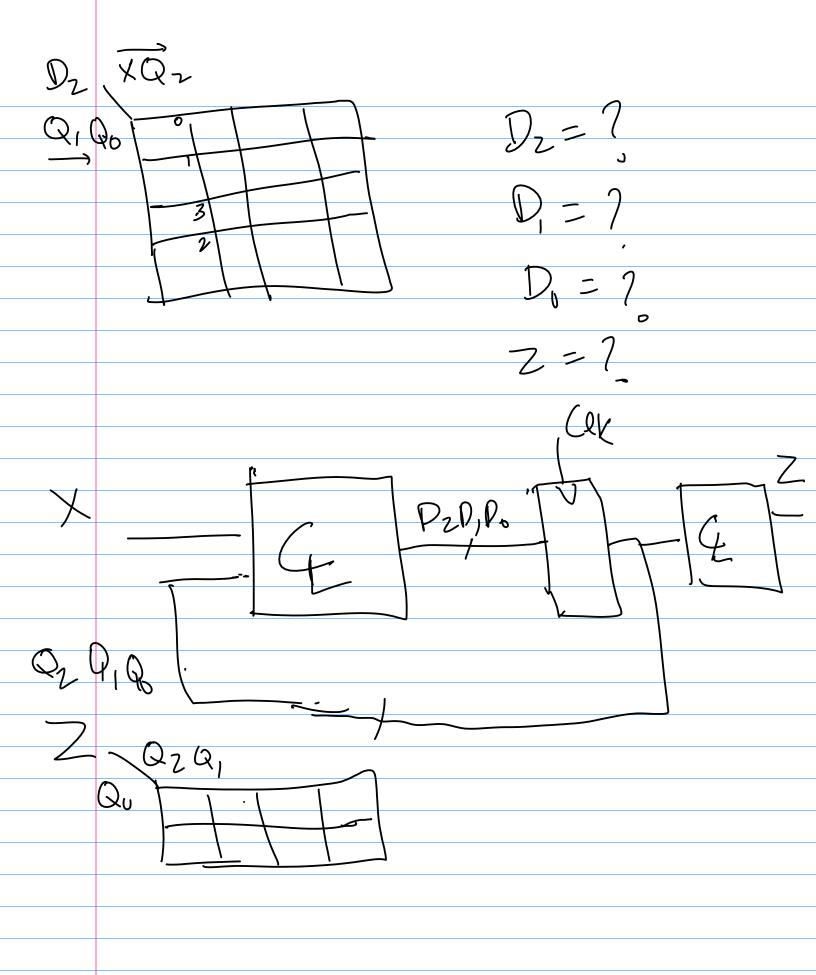

(1) Word problem E FSM (Mealy/Moore) State transition trable State assignment So= 000 5) Using (D-ff), durign a T-ff curally 5.a) Use on exchatun table (5.6) Truth table that maps from imputs +state To the ff inputs

TT input + stakes -> output

state -> output

State transition table (with assignments)

| I-nput<br>X | Present Stut | (c)               | Next stul                   | TL<br>Qt     | Output<br>Z                |

|-------------|--------------|-------------------|-----------------------------|--------------|----------------------------|

| 000000      |              | 0<br>0<br>0<br>0  | 001                         | 10000        | 0000                       |

|             |              | T D I D I O I O I | J J 0 0 1 0 0 0 0 0 0 0 0 0 | d 000 1000 1 | 0<br>0<br>0<br>0<br>1<br>1 |

D-ff

Q 6\* D

d 0 0

|  | Design | Chuul | wwy | JKff |

|--|--------|-------|-----|------|

|  |        |       |     |      |

|  |        |       |     |      |

|  |        |       |     |      |

|  |        |       |     |      |

|  |        |       |     |      |

|  |        |       |     |      |

|  |        |       |     |      |

|  |        |       |     |      |

|  |        |       |     |      |

|  |        |       |     |      |

|  |        |       |     |      |

|  |        |       |     |      |

|  |        |       |     |      |

|  |        |       |     |      |

|  |        |       |     |      |

|  |        |       |     |      |

|  |        |       |     |      |

|  |        |       |     |      |

|  |        |       |     |      |