## Sequential logic design

## Vikas Dhiman for ECE275

December 5, 2022

## 1 Objectives

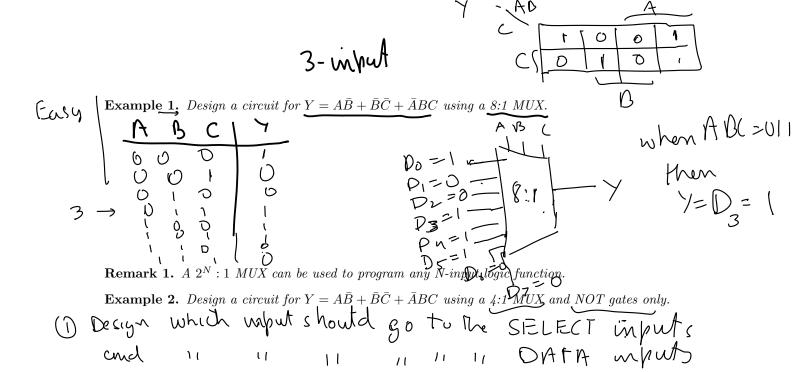

- 1. Design combinational circuits using multiplexers and decoders

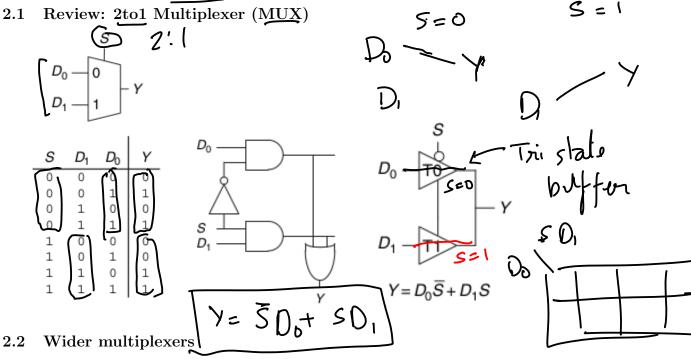

- 2 Design combinational circuit using multiplexers [1, Section 2.8.1] 2.8.2

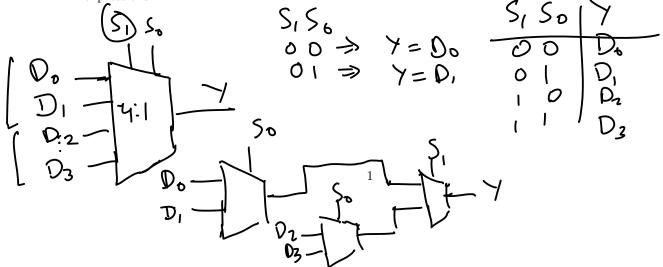

Draw the symbol for a 4:1 MUX, an 8:1 MUX and a  $2^N:1 \text{ MUX}$  and write corresponding Boolean expressions.

only I initems Y = 5, 50 D can be true + S, S, D, at a time. + S, & D2 The menter on that +5,50 D3 is true, selects the data line Minterms:  $\overline{S_1}$ ,  $\overline{S_0}$ ,  $\overline{S_$ The minterm that is true, selects the corresponding data line. 8:1 MUX Draw a symbol, write an expression and T How many select lines! Y= 525, So Do + 5,5, S, D, 5, 5, 50

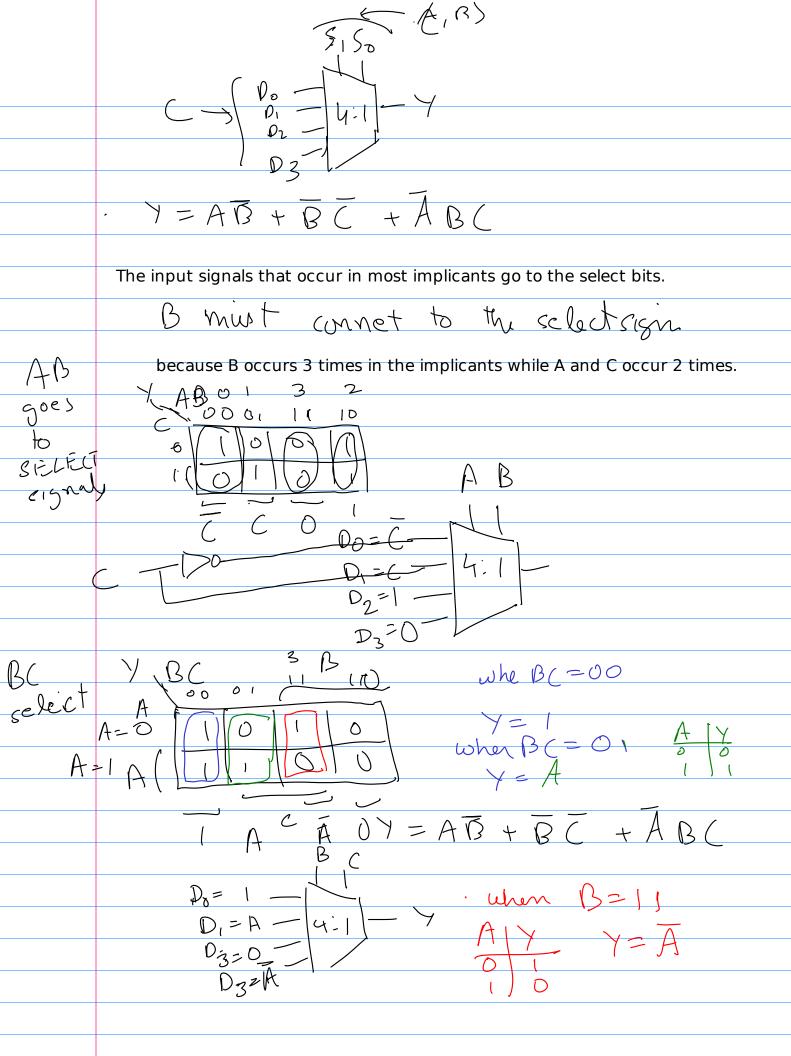

**Remark 2.** A  $2^{N-1}$ : 1 MUX can be used to program any N-input logic function, if we use literals on the input side.

**Example 3.** Design a circuit for  $Y = \bar{A}C + \bar{A}B + B\bar{D}$  using a 8:1 MUX and NOT gates only. Also design using 4:1 MUX and other gates. fewest gates.

## 3 Encoders and Decoders

Example 4. Draw the symbol and the truth table for 2:4 decoder. Also write the logic expressions.

**Example 5.** Draw the symbol and the truth table for 3:8 decoder, 4:16 decoder and  $N: 2^N$  decoder. Also write the logic expressions.

1 ) ٥ when BC=00 Y= f(A,D)=? Y= A+D when B (= 0 0 (3  $\mathcal{O}$  $\mathcal{D}_{\mathcal{O}} =$ 4:1