# Sequential logic design

Vikas Dhiman for ECE275

December 5, 2022

## 1 Objectives

- 1. Design combinational circuits using multiplexers and decoders

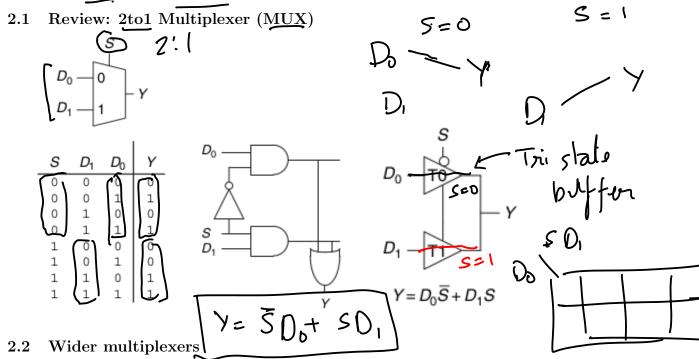

- 2 Design combinational circuit using multiplexers [1, Section 2.8.1] 2.6.2

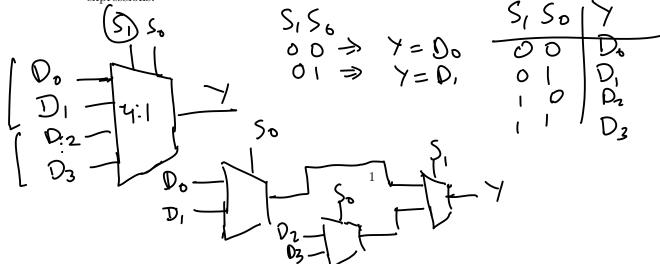

Draw the symbol for a 4:1 MUX, an 8:1 MUX and a  $2^N : 1 \text{ MUX}$  and write corresponding Boolean expressions.

only 1 mitims  $Y = \overline{S_1} \overline{S_0} D_0$ can be true + 5, 5 D, at a time. + S, 5 D2 The monter That + 5,50 D3 is true, sélecte the data lin Minterms:  $\overline{S_1} \overline{S_2}$ ,  $\overline{S_1} S_2$ ,  $\overline{S_2}$ ,  $\overline{S$ The minterm that is true, selects the corresponding data line. 8:1 MUX Draw a symbol, write an expression and T How many select Rines 525,50 Y= 525, 50 Do Do . + 5, 5, 50 V, D, S.I MUX S, S, So Dy 05 01 **9**7 525,50 Sw-1. Sa  $S_2 S_1$ 00 G 0 U  $\mathcal{O}$ Don

**Remark 2.** A  $2^{N-1}$ : 1 MUX can be used to program any N-input logic function, if we use literals on the input side.

**Example 3.** Design a circuit for  $Y = \overline{A}C + \overline{A}B + B\overline{D}$  using a 8:1 MUX and NOT gates only. Also design using 4:1 MUX and other gates. fewest gates.

### **3** Encoders and Decoders

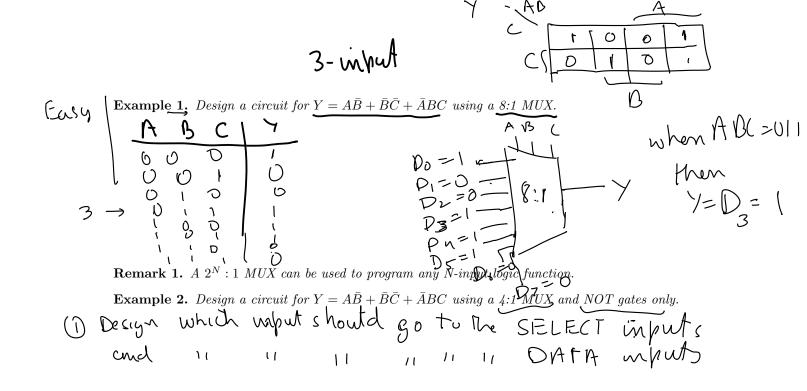

Example 4. Draw the symbol and the truth table for 2:4 decoder. Also write the logic expressions.

**Example 5.** Draw the symbol and the truth table for 3:8 decoder, 4:16 decoder and  $N: 2^N$  decoder. Also write the logic expressions.

~ (R) 5,50 Y=AB+BC+ABC . The input signals that occur in most implicants go to the select bits. B must connet to the sclect sign because B occurs 3 times in the implicants while A and C occur 2 times. AB O 2 3 goes to 0001 ID 1 (  ${}^{\circ}$ Ю SFLEC B CIGNO 4:  $\mathcal{D}_{z}^{2}$ 3 ß BC whe BC=00  $(\pi)$ select 0 1 = 0 \ Ο t ٥ Y whe A= C ÍA B  $0Y = A\overline{D}$ BC + ABC С  $\mathcal{D}_{\delta} =$ when  $D_1 = A - 4 = 1$  $D_3 = 0 - 7$  $D_3 = A$

ß BC0001 ( ) ·ct  $(\mathcal{D})$ ٥ t Ô 0  $\mathcal{O}$  $\triangleright$ when BC=00 C O A () $Y = f(A_1D) = 2$ A  $Y = \overline{A} + \overline{D}$  $\sim$ A when B(= 0 ( D  $\overline{O}$ ß when Ą 0 3 - A++  $\mathbb{O}$ ( 21 A (- AD Ь A+D  $D_0 =$ D, = 4:1 A+ Đ, D2=-**۱** = A

Example 6. Design a circuit for a XOR gate using a 2:4 decoder and an OR gate.

**Example 7.** Design a circuit for  $Y = A\overline{B} + \overline{B}\overline{C} + \overline{A}BC$  using a 3:8 decoder and an OR gate.

I

#### 3.1 Encoders

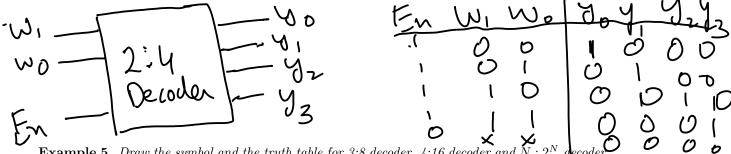

Example 8. Draw symbol and truth table for a 4:2 priority encoder.

Example 9. Draw symbol and truth table for a 8:3 priority encoder.

## References

<sup>[1]</sup> Sarah L Harris and David Harris. *Digital design and computer architecture*. Morgan Kaufmann, 2022.

2:4 ve code . 3.8 Decoder Y o WZ  $\omega_{1}$  $\omega_{1}$ Ēn - 47 En Wz W, Wa JO Y, ---J2 ·· J\_= [ -- 0 0 U  $\bigcirc$  $y_n = E_n \cdot w_2 \cdot w_1 \cdot w_0$  $U_5 = I_{2} \dots W_2 \dots W_1 \dots W_3$ mintern 5=1012 En. W2W, WO YK =

Use decoder to design court Fyb AB+AB XORgate JG ωD 02 En  $J - Y_3$ 00 - Y,=AB-Yn=AB D 1-m -y\_3 +AB

A D (c+c)->AIA BC こ + ÁBC 4 (())6 UN  $C + 4 \overline{GC}$ A B 401 O 32! 8z 14 ω Jb KM 57 A 6  $w^{0} + w^{3}$ MY 4 15

Priority Encoder  $W_2$ J 6 l 8:3 5 y y y.  $W_2 W_1 W_0 IS$ -.  $\overline{()}$  $\times$   $\times$ . ۲ **b** 0 -- ` 0  $\times x$  $\boldsymbol{\times}$  $\mathcal{O}$ •• 0 0 () $\overline{()}$ X Û I ----X 0 | \_\_\_\_X  $\bigcirc$  $W_{7} =$